Ceci est une ancienne révision du document !

Hardware - PLD, CPLD

[Mise à jour le 10/8/2022]

- Ressources

1. Définition

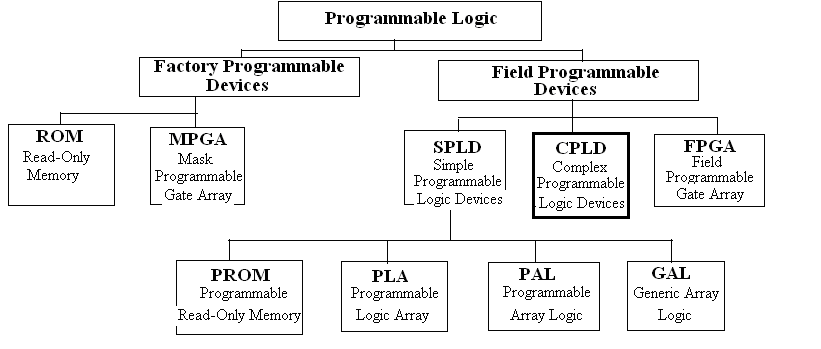

2. Classification

Ce type de composant électronique est communément désigné par différents sigles anglais dont :

- FPGA (field-programmable gate array, réseau de portes programmables in situ) ;

- PLD (programmable logic device, circuit logique programmable) ;

- EPLD (erasable programmable logic device, circuit logique programmable et effaçable) ;

- CPLD (complex programmable logic device, circuit logique programmable complexe) ;

- PAL (programmable array logic, réseau logique programmable) ;

- PLA (programmable logic array, réseau logique programmable).

3. Organisation

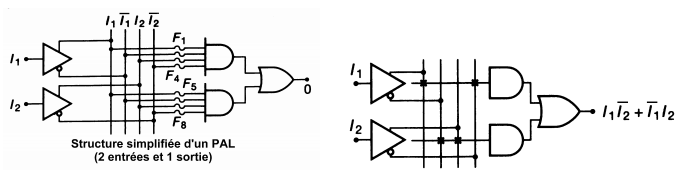

- PAL (réalisation d'un OU-Exclusif)

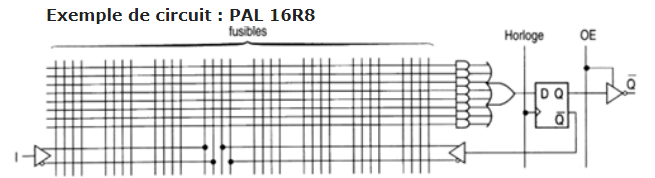

Exemple de circuit PAL16R8

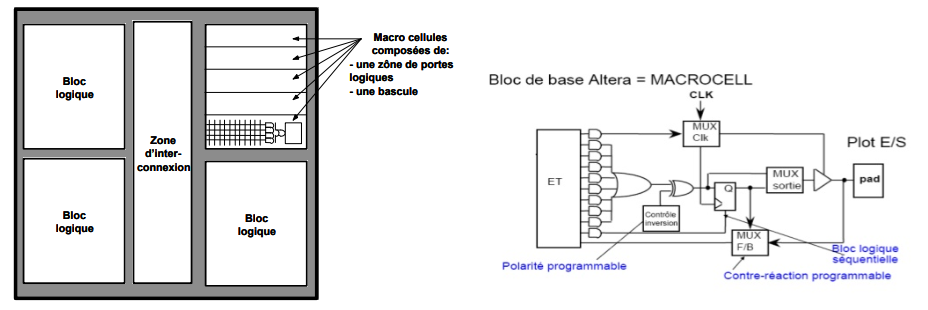

- CPLD

4. Programmation

La programmation des PLD modernes (FPGA / CPLD) passe généralement par un compilateur basé sur un langage de programmation de type langage de description matériel (ou « HDL » pour Hardware Description Language) comme le ABEL1). Pour faciliter la programmation, il existe aussi des langages de plus haut niveau. Les deux plus connus sont le VHDL2) (“V” pour “Very high speed”) et le VERILOG3).

5. Utilisation

Pour de moyennes séries, les composants programmables sont en général préférés aux ASIC. Les PLD peuvent être programmés par l’utilisateur (bureau d’étude, chaîne d’assemblage) alors que les ASIC qui sont configurés lors de leur fabrication (ils ne peuvent être que simulés par le bureau d’étude) sont réservés à des productions de très grande série ne serait-ce qu’en raison de leur coût de développement élevé.