Hardware - PLD, CPLD

[Mise à jour le 11/8/2022]

- Ressources

- Vidéo PLA PAL GAL CPLD sur YouTube

1. Définition

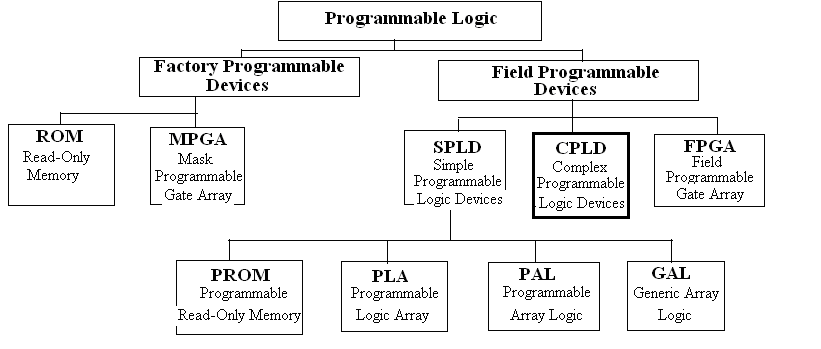

2. Classification

Ce type de composant électronique est communément désigné par différents sigles anglais dont :

- FPGA (field-programmable gate array, réseau de portes programmables in situ) ;

- PLD (programmable logic device, circuit logique programmable) ;

- EPLD (erasable programmable logic device, circuit logique programmable et effaçable) ;

- CPLD (complex programmable logic device, circuit logique programmable complexe) ;

- PAL (programmable array logic, réseau logique programmable) ;

- PLA (programmable logic array, réseau logique programmable).

3. Organisation

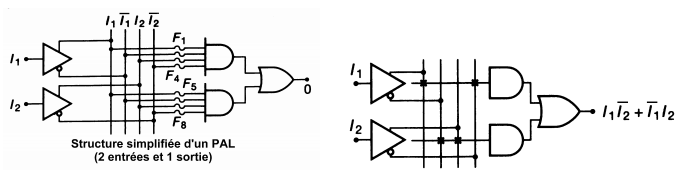

- PAL (réalisation d'un OU-Exclusif)

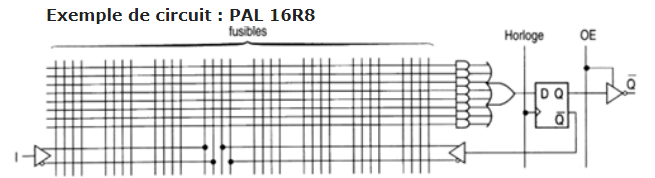

Exemple de circuit PAL16R8

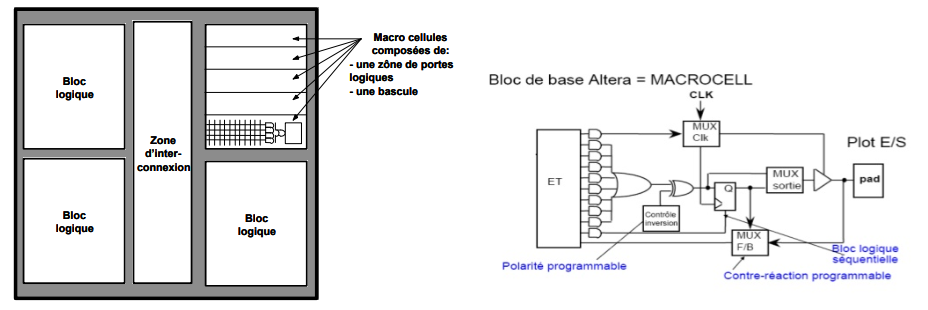

- CPLD

4. Programmation

La programmation des PLD modernes (FPGA / CPLD) passe généralement par un compilateur basé sur un langage de programmation de type langage de description matériel (ou « HDL » pour Hardware Description Language) comme le ABEL1). Pour faciliter la programmation, il existe aussi des langages de plus haut niveau. Les deux plus connus sont le VHDL2) (“V” pour “Very high speed”) et le VERILOG3).

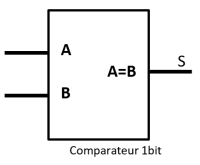

Exemple : comparateur logique

Code VHDL d'un comparateur 1 bit

Code VHDL d'un comparateur 1 bit

- Description structurelle

- *.vhdl

--Importation des bibliothèques library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; -- Description de l'interface externe entity COMPARATEUR1bit is port( A,B : IN STD_LOGIC; S : OUT STD_LOGIC; end COMPARATEUR1bit; -- Description structurelle architecture EQU_LOG of COMPARATEUR1bit begin S <= not(A xor B); end EQU_LOG;

- Description fonctionnelle

- *.vhdl

-- Seule la partie description du code ci-dessus est modifiée architecture COMPORT of COMPARATEUR1bit begin S <= '1' when A=B else '0'; -- C'est intuitif, concis et clair ! end COMPORT;

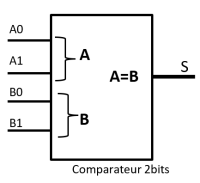

Code VHDL d'un comparateur 2 bits

Code VHDL d'un comparateur 2 bits

- Description structurelle

- *.vhdl

--Importation des bibliothèques library IEEE; use IEEE.std_logic_1164.all; use IEEE.numeric_std.all; -- Description de l'interface externe entity COMPARATEUR2bits is port( A,B : IN STD_LOGIC_VECTOR (1 dowto 0); -- A et B sont des mots de 2bits : A = A1A0 et B = B1B0 S : OUT STD_LOGIC; end COMPARATEUR2bits; -- Description structurelle architecture EQU_LOG of COMPARATEUR2bits begin S <= ( not(A(1)) and not(A(0)) and not(B(1)) and not(B(0))) or (not(A(1)) and A(0) and not(B(1)) and B(0)) or (A(1) and not(A(0)) and B(1) and not(B(0))) or (A(1) and A(0) and B(1) and B(0)); end EQU_LOG;

- Description fonctionnelle

- *.vhdl

-- Seule la partie description du code ci-dessus est modifiée architecture COMPORT of COMPARATEUR2bits begin S <= '1' when A=B else '0'; -- Identique au comparateur 1bit et généralisable à n bits !!! end COMPORT;

5. Utilisation

Pour de moyennes séries, les composants programmables sont en général préférés aux ASIC. Les PLD peuvent être programmés par l’utilisateur (bureau d’étude, chaîne d’assemblage) alors que les ASIC qui sont configurés lors de leur fabrication (ils ne peuvent être que simulés par le bureau d’étude) sont réservés à des productions de très grande série ne serait-ce qu’en raison de leur coût de développement élevé.